ハードウェアトロイとは? LSIに隠された不正回路を検知する技術に迫る

スパイウェアの代表格である「トロイの木馬」は、セキュリティに関心のある方ならご存じだろう。システムに潜伏し、あるきっかけで活動を開始し、システム内の情報を外イブ外部に流出したり、改ざん、破壊活動を行ったりする厄介なマルウェアだ。そのハードウェア版「ハードウェアトロイ」が猛威を振るいつつある。

目次

- ハードウェアトロイとは何か

- ハードウェアトロイはどうやって組み込まれるのか

- ハードウェアトロイを検出する方法は?

- ハードウェアトロイの主な特徴

- 3つの代表的なハードウェアトロイの検出方法と「弱点」

- 回路のパターンマッチングによる検出技術

- 機械学習を応用したパターンマッチングによるハードウェアトロイ検出

ハードウェアトロイとは何か

ハードウェアトロイは、半導体チップ(LSIなどの集積回路)に本来の機能とは別の回路を仕込み、特定の入力などのトリガーとなる事象が生じた場合に不正な活動を行う。2013年には中国からロシアに輸出された電気アイロンに不正な回路が組み込まれ、周囲の暗号化されていない無線LANを利用しているPCにマルウェアを送り込んで多量のスパムメールを送信する事件が起きている。はっきりと悪意をもった不正行為としてクロ認定されているのはこれだけだが、ハードウェアトロイが組み込まれたと疑われるチップは電気ケトル、スマートフォン、自動車、カメラ、人形などからも発見されている。さらには軍事攻撃に備える監視レーダーの部品にレーダーを停止させる回路が組み込まれていたという未確認情報さえある。こうした事案には、チップそのものが不正活動を意図して作られたと思われるものもあれば、不正回路の存在に気付かず製品にチップを組み込んでしまったものもあるのではないかと思われる。

ハードウェアトロイはどうやって組み込まれるのか

そもそも最初のチップ仕様記述時点から悪意をもって不正回路を組み込むこともできるが、チップメーカーには悪意がない前提で考えると、次の経路で不正回路が混入される可能性がある。

- チップ設計用ツール(設計ソフトウェア)

- セルライブラリ(回路パーツ。機能ブロック=マクロセルの設計情報データベース)

- 設計済みの機能ブロック(動作確認済みの設計資産=IP(Intellectual Property))

- 製造工程でのマスク(回路パターンの転写用原版)

- ファブリケーション(回路パターン形成工程)

- パッケージング(回路を筐体に組み込む製造最終工程)

(1)の設計用ツールは海外製のものが利用されており、(2)(3)の回路パーツは自社内のもの以外に外部から入手するものが多い。(4)以下の製造工程も外部委託されることがある。チップメーカーは仕様に基づき(1)〜(3)のツールや設計情報を使って、チップ設計用のハードウェア記述言語(Verilog HDLやVHDLなど。記述されたものをRTL記述という)で設計する。設計の後工程は工場で実作業が行われるが、(4)〜(6)の現場工程で不正回路が組み込まれる可能性がある。

不正回路の混入タイミングとしておおまかには、図1の2つのポイントがあることになる。

また、FPGA(Field-Programmable Gate array)などでは、チップ製造後にユーザー(機器メーカーなど)が一部の回路を再構成できる(プログラマブル)ため、チップメーカーの最終製品がクリーンであっても、後から不正回路を構成されることも考えられる。

現在では何らかの電子機器は、情報処理のコア部分であっても単一メーカーの部品だけで組み立てられることはほとんどなくなり、基板上に複数の海外製部品が組み付けられるのが普通だ。一般的にはどの部品も製造者や製造時期などが特定できるトレーサビリティーがあるとはいえ、部品メーカーでさえ気付かずにハードウェアトロイが存在する製品を流通させてしまう可能性がないとは誰にも言えない。

ハードウェアトロイを検出する方法は?

ではチップに忍び込んだハードウェアトロイをどうやって見つければよいのだろうか。ここからは、まずハードウェアトロイの特徴を確認し、主要な検出手法を見ていく。

ハードウェアトロイの主な特徴

ハードウェアトロイの主な特徴は、大きく分けて2つ挙げられる。1つは、集積回路全体から見れば「ごく小さな規模の回路」であることだ。

あまりに複雑で大規模な回路だとチップサイズが大きくなり、チップメーカーなどが不審に思う可能性があるため、存在を隠すために小規模にする。そのため目視では正当なチップと判別がつかない。小規模な回路は高度なネットワーク制御のような活動はできないが、それでも暗号化を担うチップが特定データを暗号化せずに送出したり、暗号鍵を送出したりすることくらいは簡単だ。攻撃者はその情報を得て、深刻な被害を生じさせる攻撃を準備、実行することができる。

もう1つの特徴は、通常は不正な活動を行うことなく、何らかの特定の入力や回路の内部状態の変化をきっかけに悪意ある不正な動作を開始することだ(一部には常に不正動作をするものもあるとされる)。トリガーになる入力や内部状態の変化がどのようなものなのかは予見するのが非常に難しい。

こうした特徴から、ハードウェアトロイが存在するか否かの検知は困難だが、設計段階でのトロイ挿入に関しては、幾つかの検知方法が研究されている。

3つの代表的なハードウェアトロイの検出方法と「弱点」

1つ目の検出方法は「ロジックテスト」だ。これはチップ内の回路に対する入力のパターンを大量に生成し、出力の正当性をチェックするもの。トリガーとなる入力があった場合に不正な出力が検知できるが、例えば入力の数が128bitであれば2の128乗通りの入力パターンでチェックすることになり、現実的にはコストも時間もかかりすぎて難しい。

2つ目の検出方法が「サイドチャネル分析」だ。これはハードウェアトロイが混入していないことが分かっている設計情報(ハードウェア記述言語による)と、検査対象の設計情報とを比較する方法だ。しかしハードウェアトロイが混入していないと保証できる設計情報(Golden Netlistという)は現実には存在せず、これも現在のところ使えない。

さらには3つ目の検出方法として「Post Verification」と呼ばれる手法もある。これはチップの検証プロセスで特定の入力の値が常に同じ値(0または1)になっている部分(つまりロジックとして意味がない)を見つけ、その部分に適切な入力を生成してハードウェアトロイが活性化するかどうかを判別する。こちらもシミュレーションを繰り返す方法になるため効率がよいとはいえない。ロジックテストと同様に現実的には限られた数のテストパターンでチェックするしかないので、テストパターン以外の入力がトリガーとなる可能性は消えない。

第4の検出方法:回路のパターンマッチング

そこで、これら3つのアプローチとは異なる方法として考えられたのが、回路の「パターンマッチング」によって検出する方法だ。

既に学術的に考案されているハードウェアトロイの回路構造の特徴を基に、検査対象の回路との一致を検出するものだ。この手法は早稲田大学の戸川望教授の研究チームによって開発、検証されており、現在明らかになっているハードウェアトロイの全ての構造を100%識別した実績がある。2019年7月に、この研究成果を基に東芝情報システムと共同でハードウェアトロイ検証ツールを開発、東芝の設計による実製品に適用して「誤検知がない」つまり正当なチップにハードウェアトロイが含まれていないことを確実に判別することに成功している。ここからはこの手法について、詳しく解説する。

機械学習を応用したパターンマッチングによるハードウェアトロイ検出技術

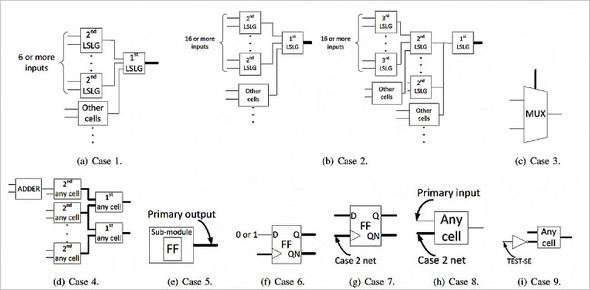

戸川教授の研究チームはまず、ハードウェアトロイを構成する回路パターンをゲートネット(信号線の集合構造)からから見つけるアプローチをとった。例えばあるゲートの前段に、不必要に多数の入力が集中するパターンは、正当な回路にはほとんどない。そのような回路はまず「怪しい」と判断できる。

既に米国の国立科学財団が運営を支援するハードウェアセキュリティに関する情報ハブである「Trust-HUB」には研究者が考案したハードウェアトロイの実例が100個近く公開されている。研究チームはそこから人力でハードウェアトロイの特徴を抽出した。その結果、ハードウェアトロイを構成する信号線の9つの特徴を抽出することができた。

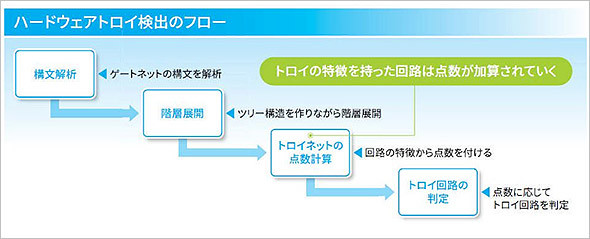

この9つの特徴に基づき、信号線の1つ1つに「怪しさのレベル」をスコアづけした。信号線の特徴それぞれの重みを点数化し、(a)の特徴を持っていたら1点、(c)の特徴を持っていたら2点、両方の特徴を持っていたら合計3点、と重み付けをする手法だ。合計点数が高ければ高いほど、ハードウェアトロイを構成する「トロイネット」である可能性が高い。スコアは最大15点とし、スコア合計が3点以上であれば確実にトロイネット、3点未満であってもスコアがついた信号線の数が5以上で、ほぼ常に一定値を出力するものも確実にトロイネットであると基準を設けた。この手法でTust-HUbのハードウェアトロイ回路を判定したところ、全ての実例を確実にハードウェアトロイであると識別できた。

この成果を受け、同技術をもとに東芝情報システムとの共同で開発した検証ツールでは、1時間程度の実行時間で実製品が検証でき、誤検知がないことが実証されている(両者は世界初の社会実装事例としている)。

ここまでは、既に既知のハードウェアトロイについて識別できたに過ぎず、未知のハードウェアトロイが発見できるわけではない。そこで戸川教授はTrust-HUBのハードウェアトロイのパターンを機械学習する手法に取り組んだ。学習する特徴量は11種類(直近入力・出力の段数やフリップフロップ数、ループ数など)とし、それぞれに重み付けをして学習を進めた。学習したのはTrust-HUBにある実例のうちの15個だ。学習の結果を使って、別の1個の実例(これを未知のものとする)が正しく識別できるかどうかを試したところ、平均66.7%の精度でハードウェアトロイを判別できた。ハードウェアトロイでない信号線については、平均99.5%の精度で識別できた。つまり非常に高い精度でクリーンな回路(ハードウェアトロイが混入していない)を識別できたことになる。

戸川教授は「ハードウェアトロイは学会でも定義が議論されている段階。悪意の存在を見破る技術はないので、現在できるのは想定外の動作をする可能性がある回路を発見することだけです。またテスト用に挿入した悪意のない回路との識別も困難です。それでも被害が起きる前にハードウェアトロイが組み込まれている可能性をアラートするのは有意義に違いありません。ソフトウェア型のトロイの木馬にアンチウイルスなどで対策しない組織は考えられませんが、ハードウェアトロイにはこれまで検知ツールがなく。全く無防備でした。検知技術のさらなる高度化や標準化、チップの正当性認証の仕組みなど、今後するべきことは多数あります。さらに。車載機器のFPGAがOTA(Over The Air)で書き換えられるような時代がもう到来しており、新たな検知技術や対策も必要になります。世界規模での取り組みが必要ですが、まずは日本から始めていきたい」と述べた。

早稲田大学と東芝情報システムは今後、ハードウェアトロイ検出手法のさらなる高度化に取り組む。また東芝情報システムは検証ツールの商用可を図っていく計画だ。

Copyright © ITmedia, Inc. All Rights Reserved.