汎用CPUの1800倍、近似アルゴリズム特化の「CMOSアニーリング」とは?:5分で分かる最新キーワード解説(3/4 ページ)

量子アニーリングとCMOSアニーリングはどう違う?

量子アニーリングの商用機(D-Wave)とCMOSアニーリング試作機の違いで特に注目したいのは、スケーラビリティの部分だ。量子アニーリングの商用機では現在のところ1素子で512量子ビットまでの処理なので、2の512乗通りの可能性の中から、現実解を、数ミリ秒で導き出せる。

一方、今回の試作機は2の20480乗通りの可能性の中から同程度の時間で現実解を導けることになる。CMOSアニーリング試作機は現在65ナノメートルプロセスという数世代前のプロセスを使っており、最新14ナノメートルプロセスで作れば16×(10の6乗)個のスピンがシミュレートできることになる。さらにチップを並列化すれば、さらに1兆スピンといった大規模化も可能とされている。

また処理に使われる電力は量子アニーリングの方が低いと考えられるのだが、その利点をはるかに上回る冷却電力が使われることに注意したい。D-Waveのプロセッサは0.02ケルビン(K:絶対温度)という極低温で動作する超電導素子だ。冷却のための設備コストとランニングコストはかなり大きくなるだろう。

一方、CMOSアニーリングは、一般的なLSIと同様のチップだ。PCやサーバの周辺機器のような形でオフィスの中に普通に置いておけるようなものになりそうだ。

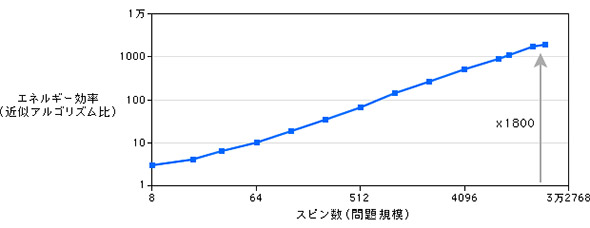

なお、日立ではSG3と呼ばれる近似アルゴリズムを、Core i5(1.87GHz、10ワット/コア)CPU上で実行したときのエネルギー効率の比較を行った。SG3と同程度の精度の解を得るために必要な時間でCMOSアニーリングを行い、同じ問題を同程度の精度で解いたときに必要としたエネルギー効率を比較した。図5に見るように、エネルギー効率は20480スピン(パラメータ数と同じ)で1800倍を記録しており、その効率はスピン数=問題規模に応じて上がっていくことが分かった。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

製品カタログや技術資料、導入事例など、IT導入の課題解決に役立つ資料を簡単に入手できます。

- ベテラン開発者が教える、サクサク動く「Pythonハック10選」 〜開発系の面白コラム集〜

- 脱Excelしたはずが、またExcelに戻る “先祖返り”を防ぐ2つの心得

- 「ChatGPT」の独走は終わった 企業が選ぶ生成AIは3強時代へ

- 超アナログ企業が2年でDXして営業利益20%アップ 直面した「3つの壁と2つの注意点」

- 福岡銀行、AI活用で年間7000時間の業務削減を目指す 契約書検索のムダを効率化

- 2027年、情報処理技術者試験が刷新 2026年終了の試験と新設のデータ試験を徹底解説

- 新人対応を「IT介護」の入口にしない 情シスが受け入れ対応で詰まる前に見ておきたい5本

- 伝説のCPU「Z80 vs. 6502」で開発者が大論争 なぜ今さらライバル対決が再燃?:879th Lap

- 資料を食わせるだけで自動化できる、「NotebookLM」の"ズルい"使いこなし術

- 経理部門は「Excel至上主義」? インボイスが“情シスの本音”に関する調査結果を発表

図5 汎用CPUでの近似アルゴリズム実行の場合とのエネルギー効率差。【条件】ランダムに生成された組み合わせ最適化問題、同じ解精度になる場合のエネルギーを比較する。イジングチップ:VDD=1.1、100-MHz、10回実行し最も精度の高い解を選択する。近似アルゴリズム:SG3をCore i5、1.87GHz、10ワット/コア上で実行(出典:日立製作所)

図5 汎用CPUでの近似アルゴリズム実行の場合とのエネルギー効率差。【条件】ランダムに生成された組み合わせ最適化問題、同じ解精度になる場合のエネルギーを比較する。イジングチップ:VDD=1.1、100-MHz、10回実行し最も精度の高い解を選択する。近似アルゴリズム:SG3をCore i5、1.87GHz、10ワット/コア上で実行(出典:日立製作所)